현재 제가 갖고 있는 4 bit ALU chip은 74LS181N입니다. 이 4 bit ALU 여러개를 연달아 붙이면 12,16,32 bit ALU가 되는데, 그러기 위해서는 CLA (Carray Look Ahead) chip인 74S182가 필요합니다.

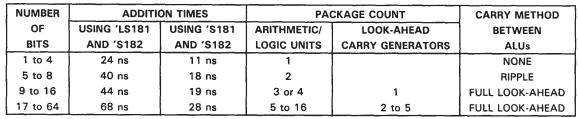

다음은 181 몇개 붙이느냐에 따라 추가적으로 들어가는 시간 지연에 대한 표입니다.

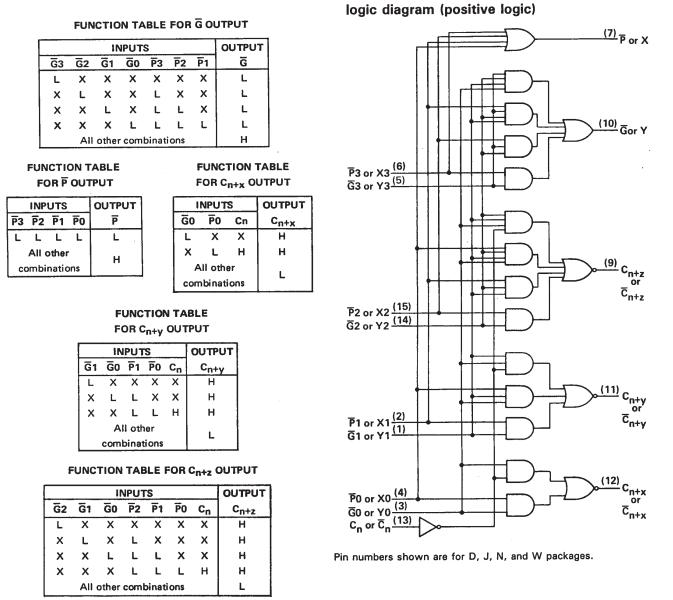

아래는 SN74S182의 datasheet에 있는 첫 페이지 핀 배열 그림입니다.

181 ALU에서 발생되는 Carry Propagate와 Carry Generate, Carry를 입력으로 받아서 진짜(?) Carry를 출력합니다.

아래는 Hansen씨가 공개한 74S182 verilog behavioral model 입니다.

CN은 Cn, CNX는 Cn+x, CNY는 Cn+y, CNZ는 Cn+z입니다.

PB는 Carry Propagate input이고 GB는 Carry Generate input인것 같습니다.

/****************************************************************************

* *

* VERILOG BEHAVIORAL DESCRIPTION OF THE TI 74182 CIRCUIT *

* *

* Function: Carry Lookahead Generator *

* *

* Written by: Mark C. Hansen *

* *

* Last modified: Dec 10, 1997 *

* *

****************************************************************************/

module Circuit74182 (CN, PB, GB, PBo, GBo, CNX, CNY, CNZ);

input[3:0] PB, GB;

input CN;

output PBo, GBo, CNX, CNY, CNZ;

TopLevel74182b Ckt74182b (CN, PB, GB, PBo, GBo, CNX, CNY, CNZ);

endmodule /* Circuit74182 */

/*************************************************************************/

module TopLevel74182b (CN, PB, GB, PBo, GBo, CNX, CNY, CNZ);

input[3:0] PB, GB;

input CN;

output PBo, GBo, CNX, CNY, CNZ;

assign PBo = (PB[0]|PB[1]|PB[2]|PB[3]);

assign GBo = ((GB[0]&GB[1]&GB[2]&GB[3]) |

(PB[1]&GB[1]&GB[2]&GB[3]) |

(PB[2]&GB[2]&GB[3]) |

(PB[3]&GB[3]));

assign CNX = ~((PB[0]&GB[0]) |

(~CN&GB[0]));

assign CNY = ~((PB[1]&GB[1]) |

(PB[0]&GB[0]&GB[1]) |

(~CN&GB[0]&GB[1]));

assign CNZ = ~((PB[2]&GB[2]) |

(PB[1]&GB[1]&GB[2]) |

(PB[0]&GB[0]&GB[1]&GB[2]) |

(~CN&GB[0]&GB[1]&GB[2]));

endmodule /* TopLevel74182b */

음 아래 데이터 시트에 각 핀의 진리표 및 로직이 나오는데 대충 비슷한거 같네요.

(사실 선이 많아 제대로 안 보았네요 ㅋㅋ.. 아래 로직의 (7) P 출력은 assign PBo = (PB[0]|PB[1]|PB[2]|PB[3]); 와 같은 정보만 보았네요 ㅎㅎ;;; )

181과 182는 아래처럼 연결하면 될듯 합니다.

예를들어 16비트 ALU를 만드려면 181 4개와 182 하나를 연결합니다.

32비트는 다음과 같이 연결합니다.

다음은 Ripple-Carry과 CLA를 혼합한 예이다.

다음은 64bit ALU예이다. (ㅎㄷㄷㄷ; )

다음은 74181 세 개와 한개의 74182를 이용한 12bit ALU를 애플릿 예제로 보여주고 있습니다.

TTL-series 74181+74182 ALU+CLA demonstration

보다 자세하게 왜 Carry만 있지 않고 Carry Propagate, Generate가 필요한지 등은 Building 32bit ALU by cascading 74181 4bit ALU blocks에서 나젤큐스님의 한글 블로그 포스트로 친철하게 소개하고 있습니다.

나젤큐스님의 32bit ALU 만들기 연재 글

Building 32bit ALU by cascading 74181 4bit ALU blocks

Building 32bit ALU by cascading 74181 4bit ALU blocks #2

Building 32bit ALU by cascading 74181 4bit ALU blocks #3

Building 32bit ALU by cascading 74181 4bit ALU blocks

Building 32bit ALU by cascading 74181 4bit ALU blocks #2

Building 32bit ALU by cascading 74181 4bit ALU blocks #3

저는 181은 eBay를 통해서 불가리아로 부터 구입했습니다;;.. 근데 도저히 182는 구할 방도가 없더군요..

그런데 생각해보니 GAL을 이용해서 182 로직을 생성해서 쓰면 되지 않을까 하는 생각이 문득들더군요.

verilog 소스도 있겠다, 쉽게 GAL 소스로 바꾼 후 테스트 해봐야 할 것 같습니다.

근데 당장은 8bit ALU를 만드는 거니까 182없이 그냥 181을 그냥 ripple carry방식으로 붙여도 될거 같네요; ㅋㅋㅋ

ps. 향후에 곱셈기도 만들어야 할지 모르겠는데...

검색하다보니 An 8-by-8 Bit Multiplier 라는 좋은 웹페이지가 걸려나오네요. 74181과 74183 (dual binary adder)를 활용하였네요.

ps2. 최소한의 TTL 프로세서 관련한 좋은 웹페이지도 있네요. 일단 엮어놔야지.

A Minimal TTL Processor for Architecture Exploration

'KB > TTL' 카테고리의 다른 글

| GAL20v8 를 활용한 4 bit counter (0) | 2009.02.02 |

|---|---|

| dip input, 7 segment, GAL test (0) | 2009.02.02 |

| 7 segment와 DIP switch 사용 (0) | 2009.01.20 |

| 오실레이터 1Mhz와 4bit 193 카운터 사용 (0) | 2009.01.20 |